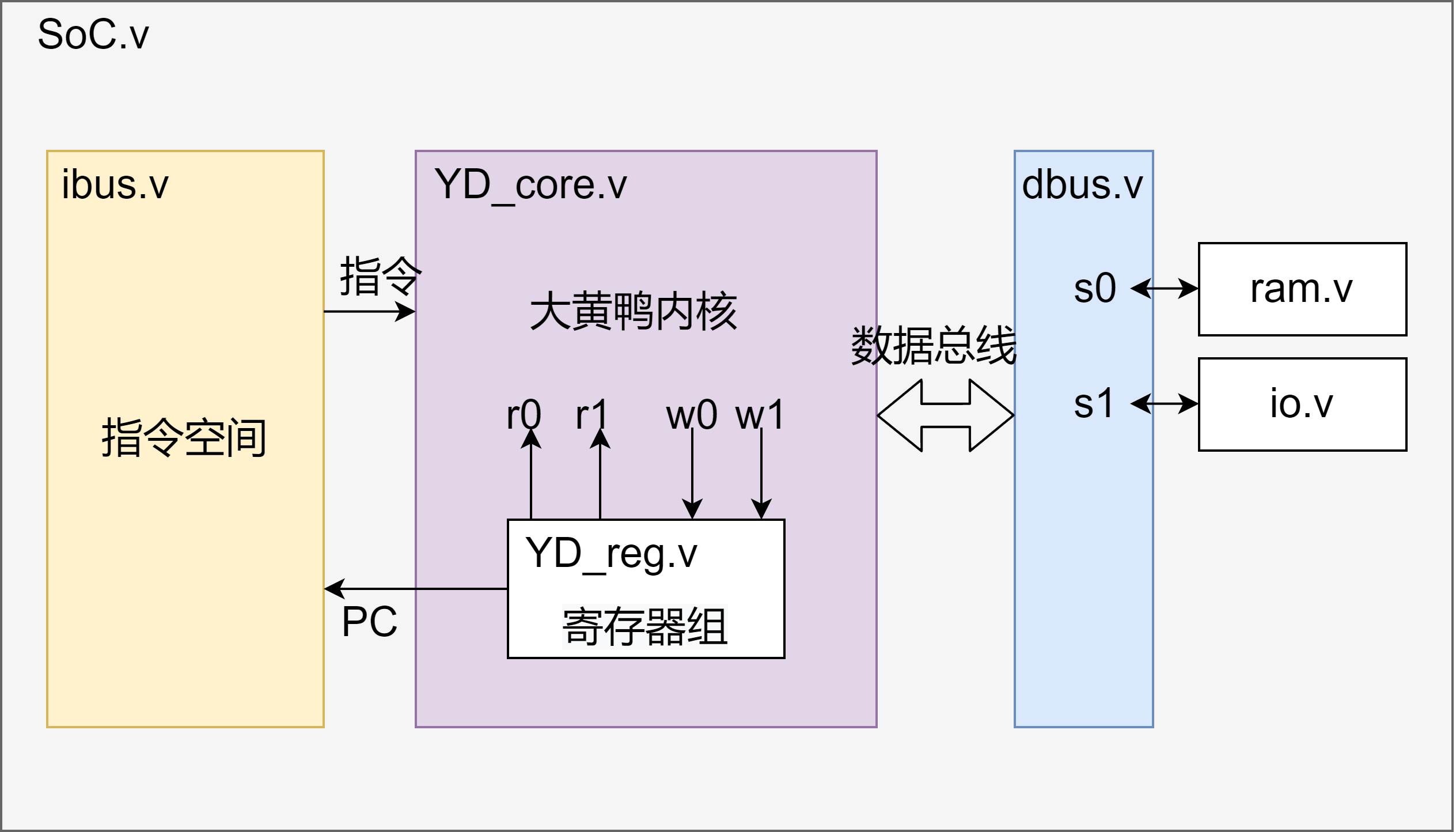

# 大黄鸭处理器的系统结构 大黄鸭处理器采用哈佛结构,指令总线连接指令空间和处理器内核,数据总线连接数据空间和处理器内核。  ### 内核 大黄鸭内核拥有16位运算位宽,16位地址线,16位指令,16位数据位宽,16个寄存器。 指令、数据空间必须且只能2字节对齐。 哈佛结构,指令地址与数据地址分离。 IO寄存器映射实现。 双发射,两条8位指令可并行执行。 2级流水线,发生跳转则使用2周期空指令填充流水线。  ### 指令总线 指令总线为16位地址位宽、16位数据位宽。 只有一个主设备(处理器内核)和一个从设备(指令空间中的指令存储器),因此可以当作没有总线,处理器内核直接访问指令存储器。 ### 数据总线 数据总线为16位地址位宽、16位数据位宽。 一主多从结构,主设备指处理器内核,从设备包含了SRAM、寄存器映射IO等多种(可能不多)外设。 数据总线把数据空间分为16个区块,地址线[15:12]用于选择区块。 每个区块有12条[11:0]地址线,16位数据位宽,可以寻址4k个单元,或者2^12x(16/8)=8kB空间。 数据总线有且只能有一个主设备,所有通信由主设备发起。主设备同时只能访问一个区块,所有区块的读写时序必须一致。。